Prototype 1

The first PIC prototype is designed with the idea of fighting obsolescence in the long term and to minimise the reaction time in the scope of HL-LHC project as the PIC should be connected to the PDSUs monitoring the CLIQ units. Indeed, in case of a spurious firing of on CLIQ unit, the beam has to be dumped in the 470 usec maximum, letting a maximum reaction time of the PIC of 80 usec.

The proposal is to design a full industrial system keeping the same hardware architecture as for the current operational PIC and:

- to replace the current Siemens S7-300 PLC series which is at the end of its life, with its descendant, the S7-1500 series,

- to design the QPS and PC interfaces with industrial optocouplers,

- to renew redundant power supplies for the PLC,

- to use a fast PLC from B&R (1 usec reaction technology) instead of the current obsolete CPLD for the beam dump function.

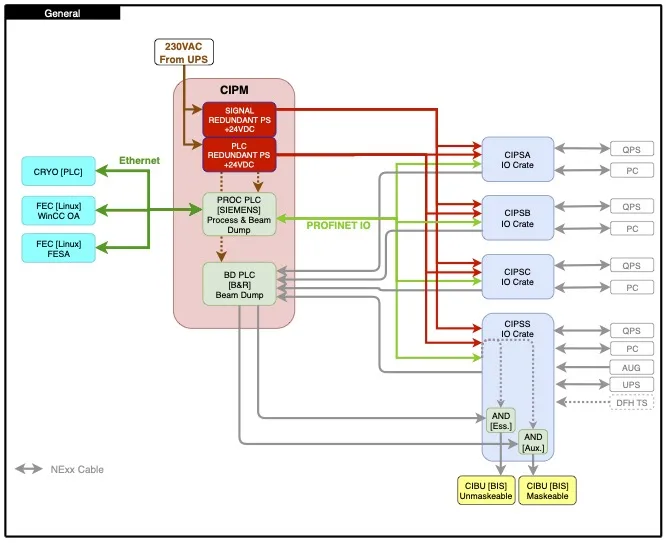

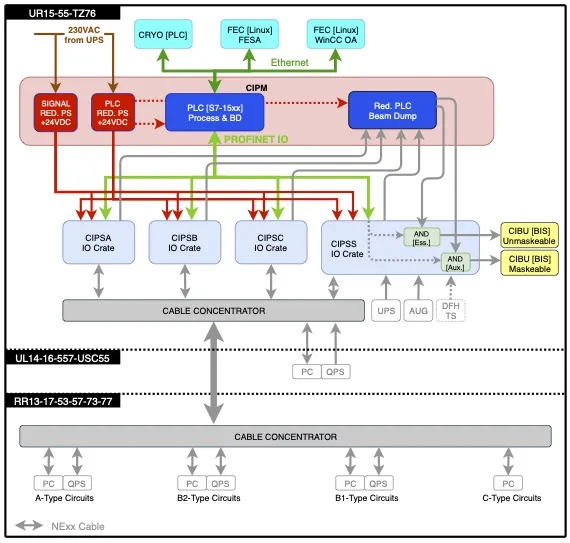

Concept

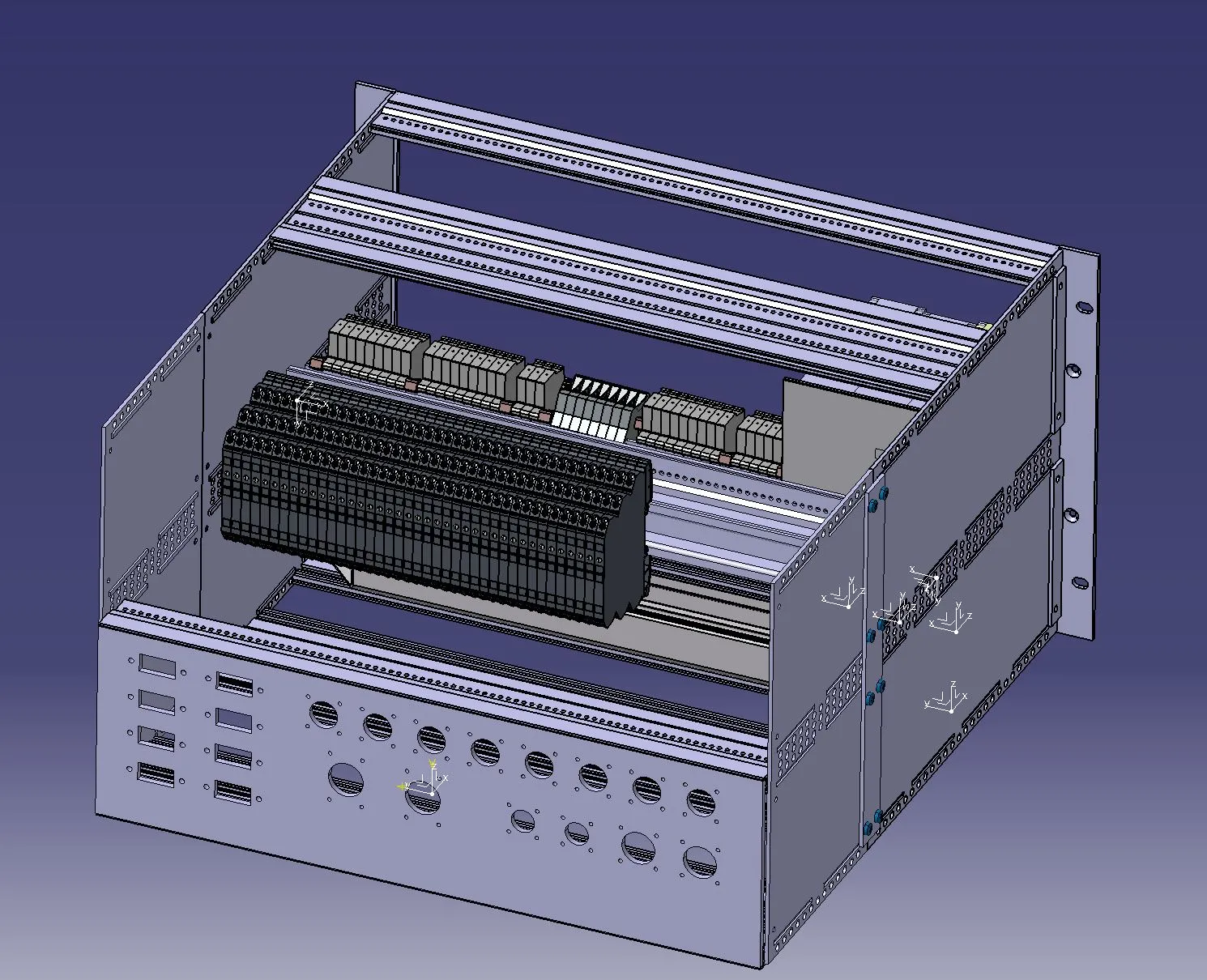

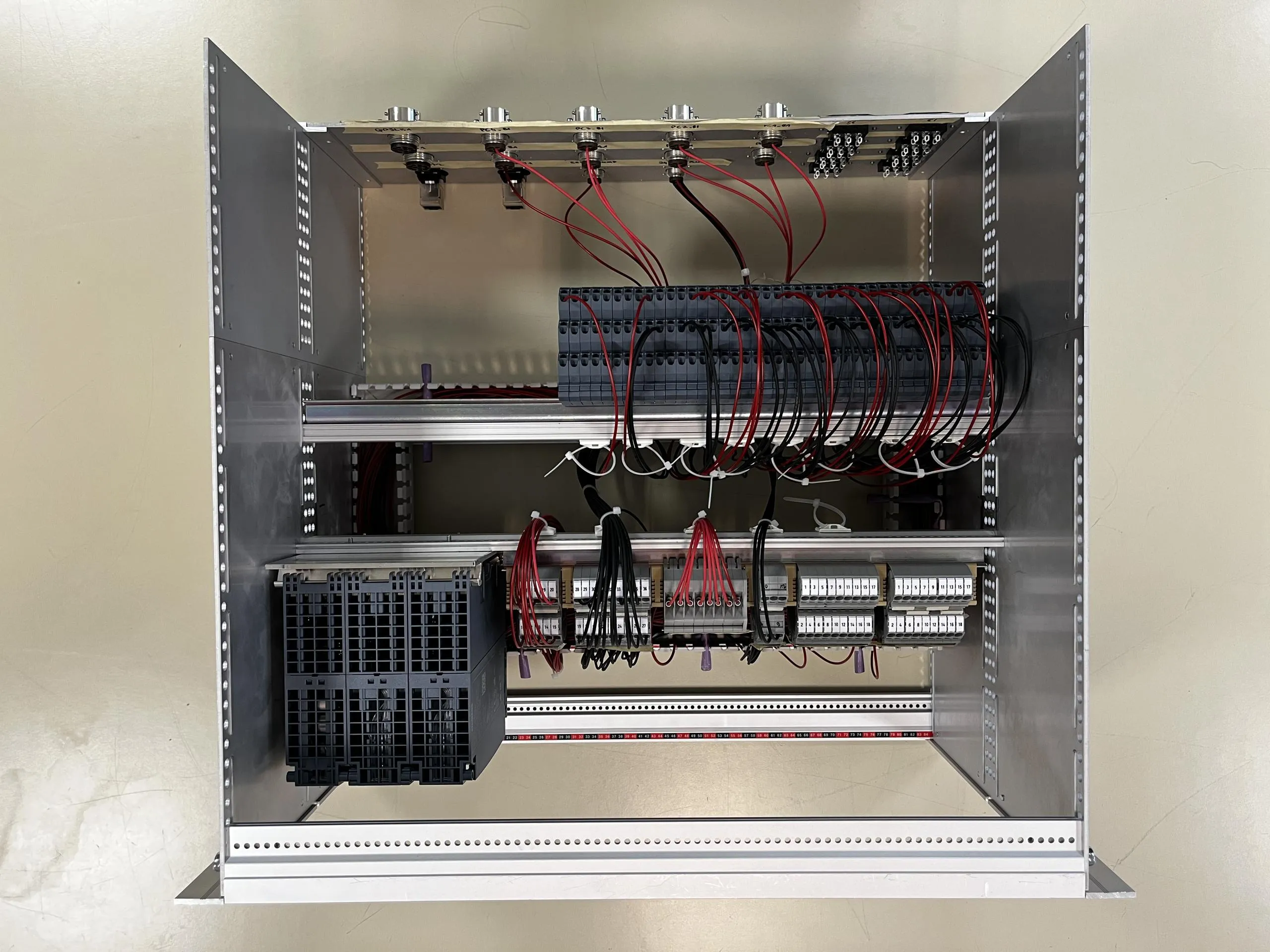

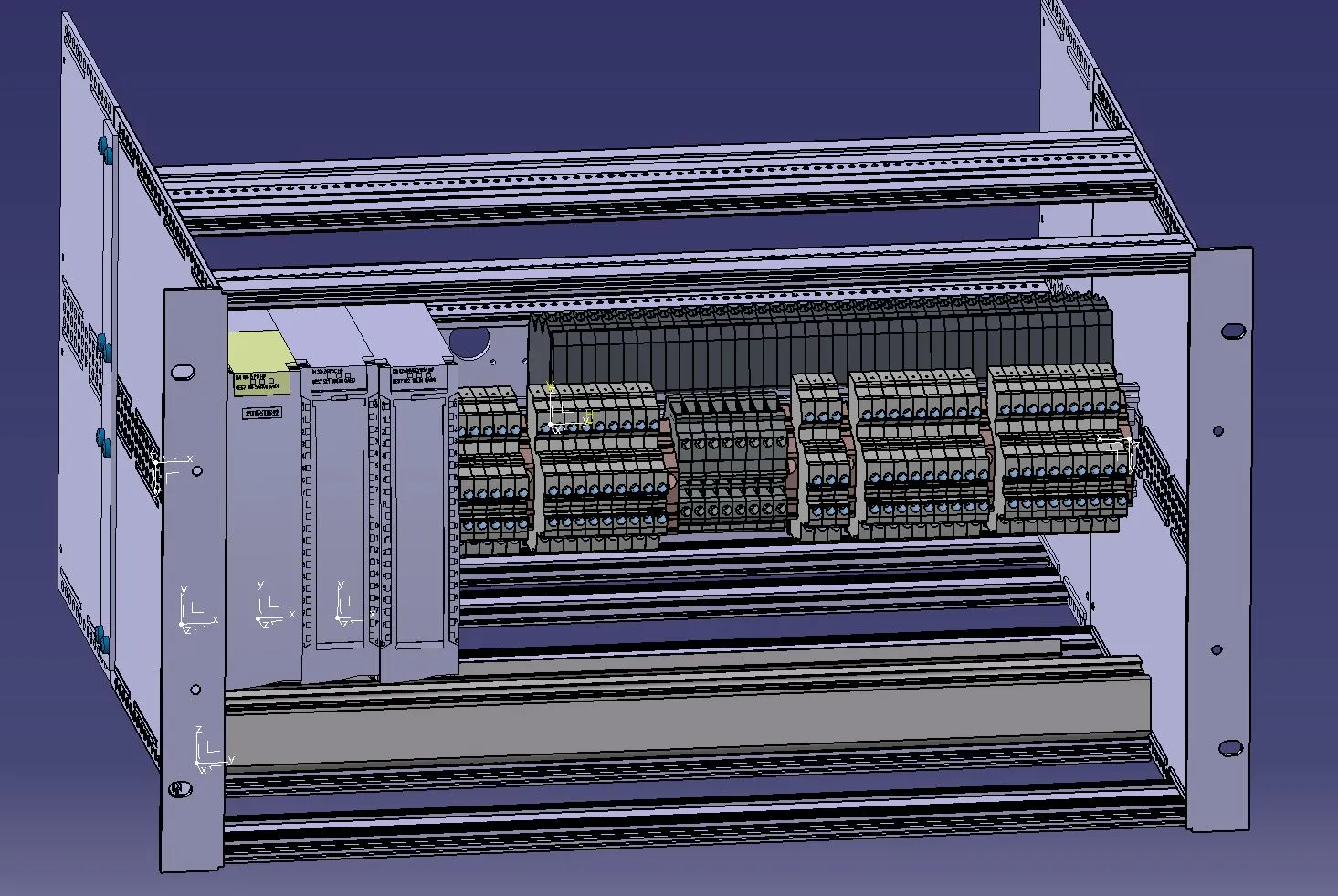

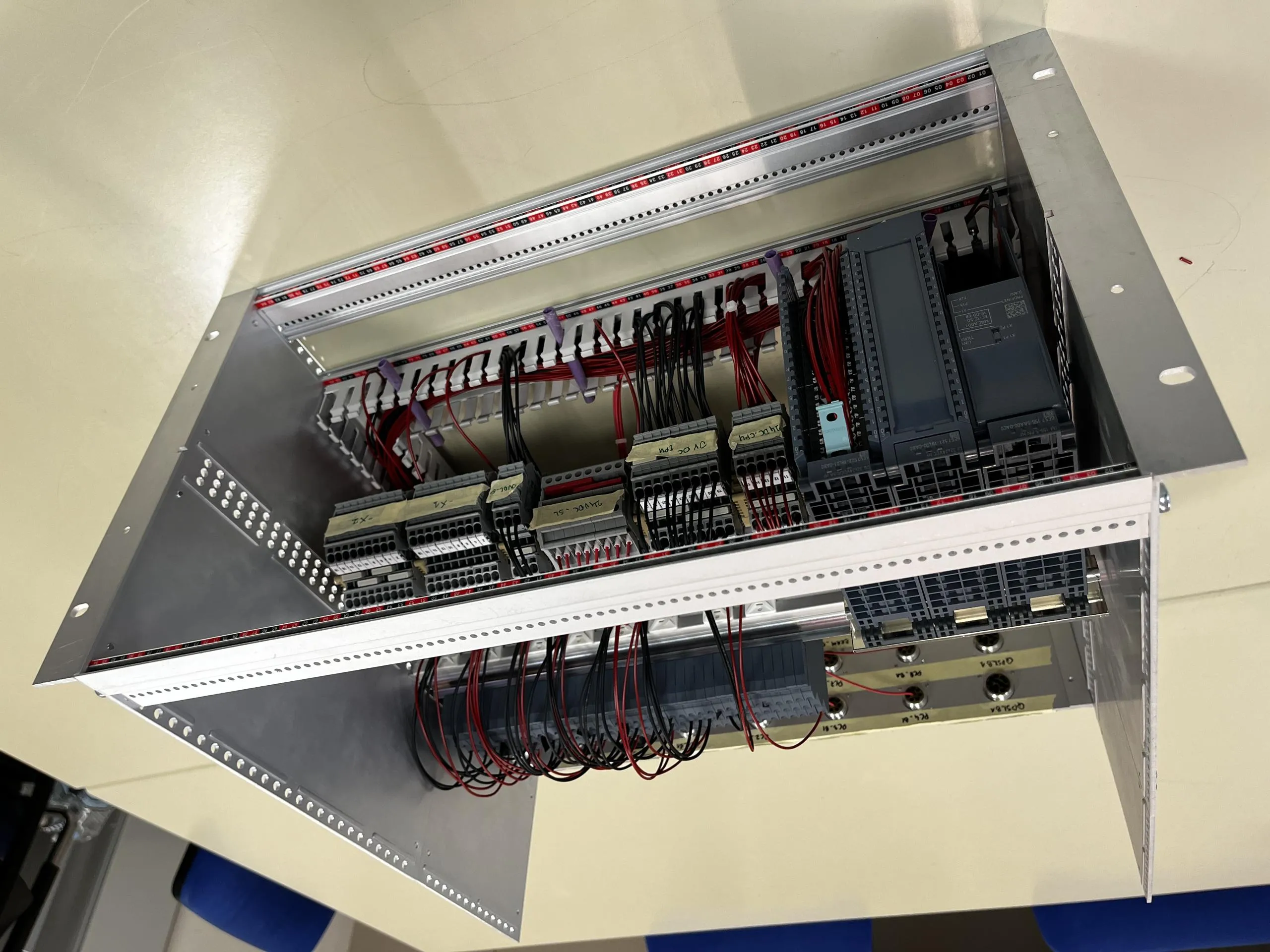

The PIC will be based on the PLC technology with two different types of PLC. A master crate housing two Siemens S7-1500 family CPU (CIPM) which are connected to deported I/O slaves through two individual profitNet fieldbus. One CPU is dedicated to the full process while the second one is only dedicated to the beam dump functionality. To be able to interface all circuits in all LHC powering subsector, only two slave crates are necessary: the CIPSA and the CIPSB crates. A power crate (CIPS) to supply all crates with 24 VDC as well as a crate to get all thermal switches from the DFHX and DFHM at LHC point 1 and 5 (HL-LHC) complete the PIC Prototype 2 portfolio.

All crates are designed from a standard 6U, 19" crate from SCHROFF. In particular, the CIPSA and CIPSB house two Siemens ET200MP I/O deported slaves (for redundancy) on the front connected to sliding tailor-made electronic boards through an electronic backplane and flat cables.

|

|  |

|

CIPSB slave crate design | |||

Control Architecture

| crate TYPE A | ||||

| TYPE B |